#### Photon imaging with monolithic CMOS SPADs

<u>Ajit Kumar Kalgi</u>, Benoit Dupont, Bart Dierickx, Nick Witvrouwen Caeleste, Generaal Capiaumontstraat 11, 2600 Antwerp, Belgium

www.caeleste.be

Presented at "CMOS Image Sensors for High Performance Applications" Toulouse, Nov 2013

#### Purpose

#### Why a 2D array of monolithic SPADs?

Mainly for applications requiring precise information of the time of arrival of the photon. e.g.

- Photon counting

- Coincidence detection

- Time Of Flight imaging, distance ranging, approach, docking

- Fluorescence decay

- Spectroscopy

- > X-ray, gamma, HE particle detection

**Our specific goal**

to explore tunability of performance parameters

> QE(Quantum Efficiency)

> DCR(Dark Count Rate)

> After pulsing time

> In std 0.18µm technology

#### Outline

# Introduction: The SPAD principle Layout of SPAD and SPAD arrays Measurement results Conclusions

#### Outline

# Introduction: The SPAD principle Layout of SPAD and SPAD arrays Measurement results Conclusions

2 December 2013

#### **The SPAD principle**

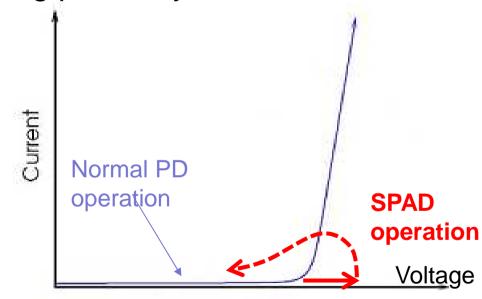

#### SPAD or "Geiger-Mode" APD

#### - Operating point beyond breakdown voltage

2 December 2013

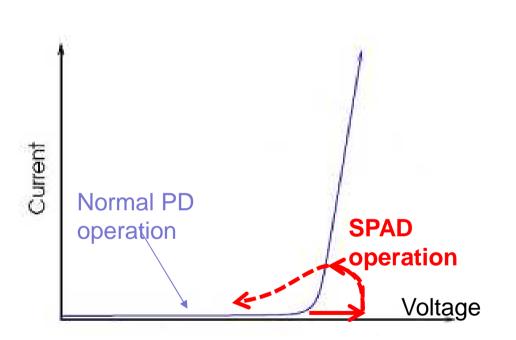

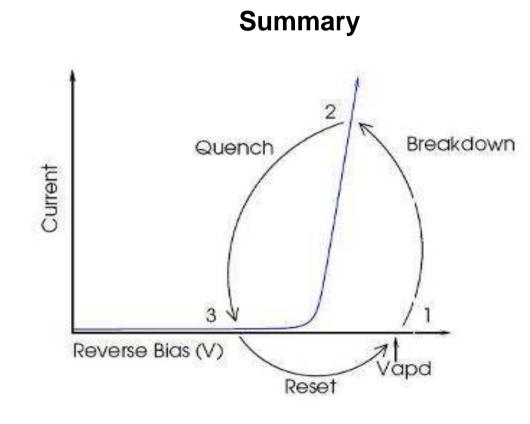

### **SPAD** background

- Recharge (Reset):

- Voltage beyond the breakdown value is applied and stays there until...

- Sense:

- An electron (due to photon/dark current) causes breakdown and hence a huge current.

- The drop in voltage is sensed with appropriate analog circuitry.

- Discharge (Quench)

- Residual charges are drained out completely.

2 December 2013

#### **SPAD** background

Caeleste SPAD technology

**SPAD circuitry**

#### Outline

# Introduction: The SPAD principle Layout of SPAD and SPAD arrays Measurement results Conclusions

#### **SPAD LAYOUT**

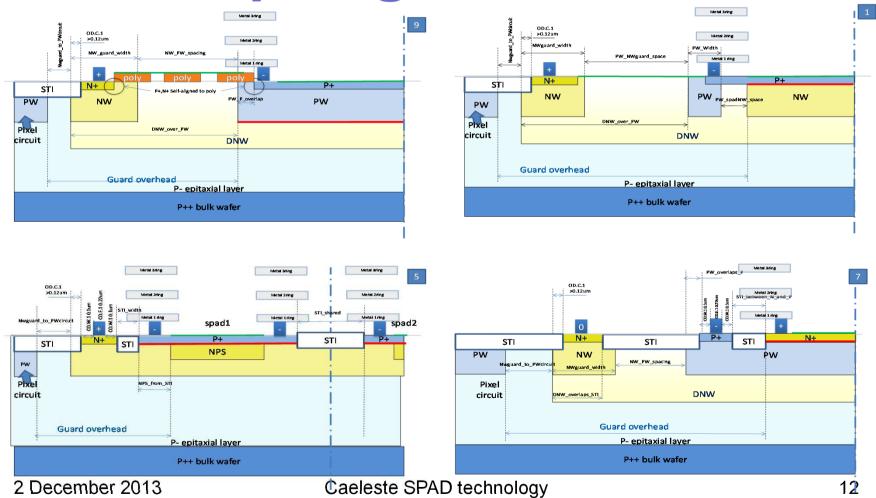

#### > SPAD topologies

• How to use available layers in the CMOS process to create SPADs and their guard rings

#### > SPAD array

• Create a complete 32x32 SPAD pixel image sensor

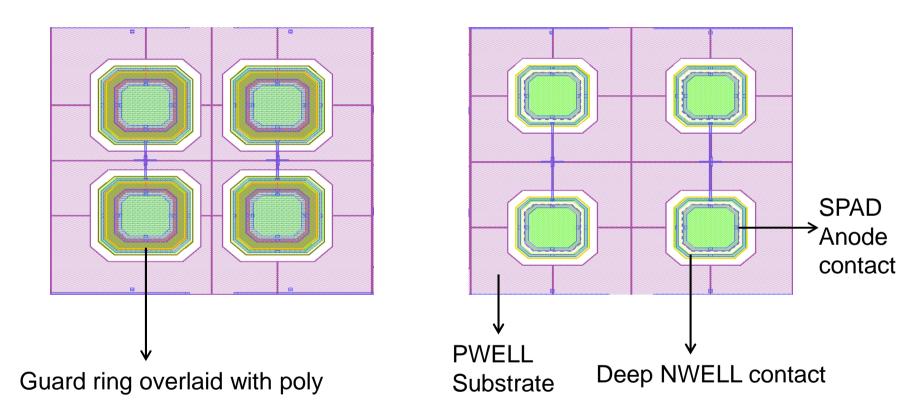

#### SPAD pixel layout

• Geometry, spacing, combination with in-pixel logic

#### > SPAD variants

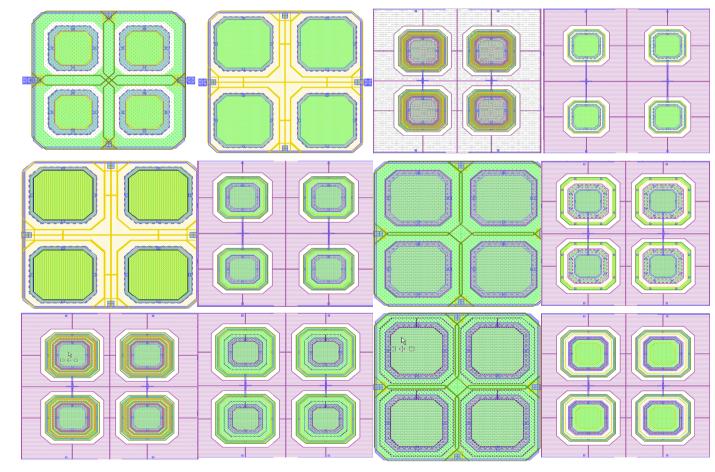

- 7 different topologies, 5 different guarding types, sharing or not sharing guards, cathode or anode readout, dimensions

- In total 120 variants

2 December 2013

#### **SPAD topologies**

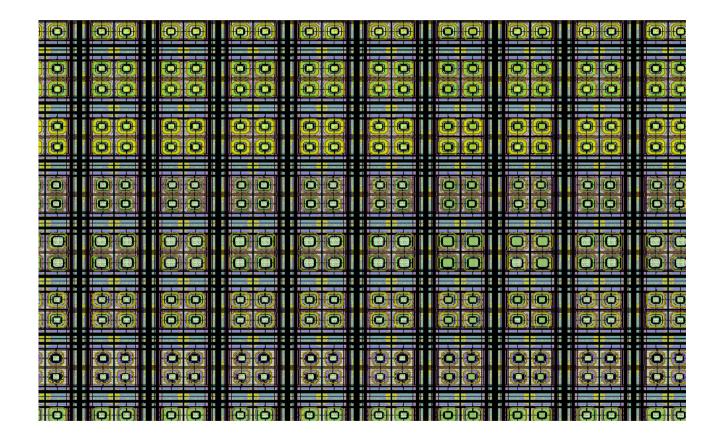

#### **SPAD** array

2 December 2013

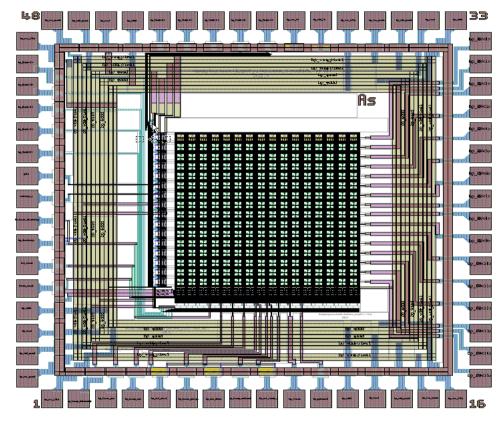

## SPAD array prototype Caeleste

- 32x32 pixels

- 16 types (variants) per such array (frame) organized per 2 rows.

- Each 2 rows of SPADs can be independently biased

- In-pixel circuitry: reset, quench, analog domain counter, analog output, application specific operators.

- 17 such arrays ("frames") are designed with different variants pixels

2 December 2013

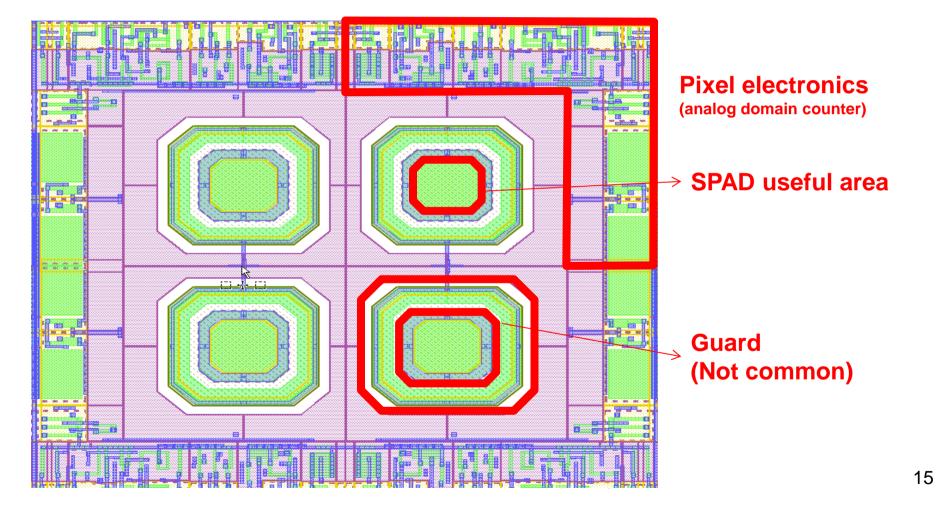

## SPAD 2x2 pixel layout Caeleste

#### **Layout Variants**

## **Other SPAD Variants** Caeleste

2 December 2013

#### Outline

# Introduction: The SPAD principle Layout of SPAD and SPAD arrays Measurement results Conclusions

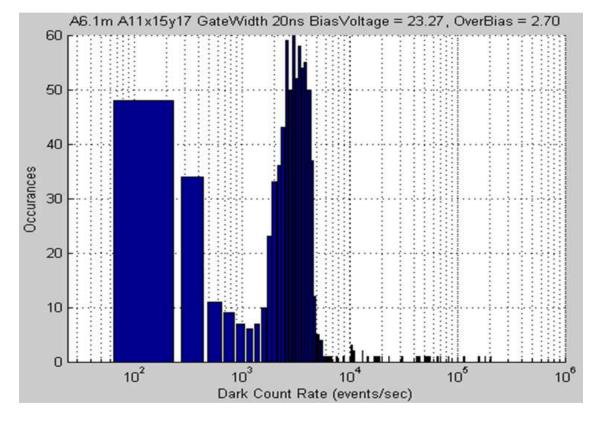

#### Measurement results Caeleste Dark Count Rate (DCR)

2 December 2013

Caeleste SPAD technology

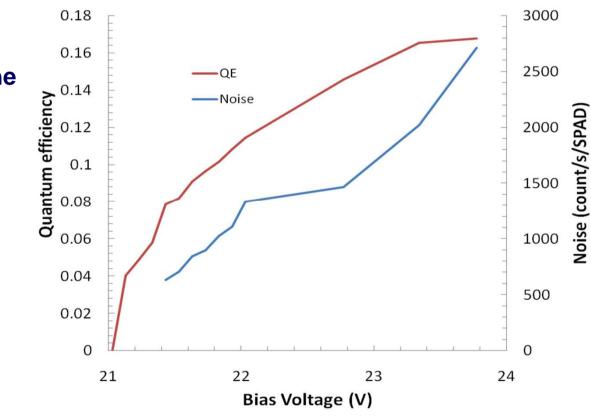

#### **QE measurement I:** Cathode connected SPAD

- Threshold voltage: 21.1 V

- Over bias up to 2.74 V in the measurement

- Max QE is >16%

- Noise = dark count rate

- 660 nm laser

Caeleste SPAD technology

caeleste

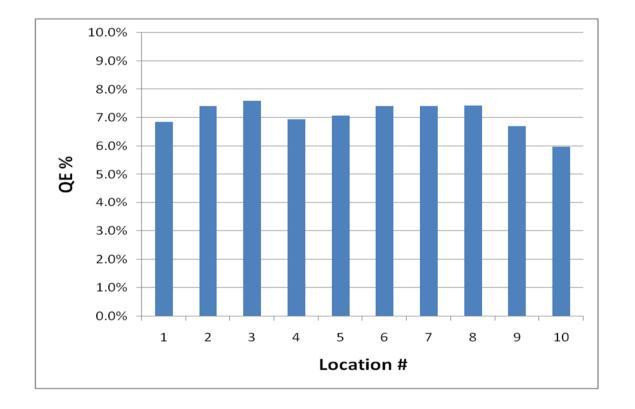

## QE at different locations

10 same pixels in the frame

QE mean = 6.7%QE STDEV = 0.49%

The variation is quite low: STDEV/mean = 6.8%

Bias Voltage 21.43 V (Threshold voltage 21.1 V)

2 December 2013

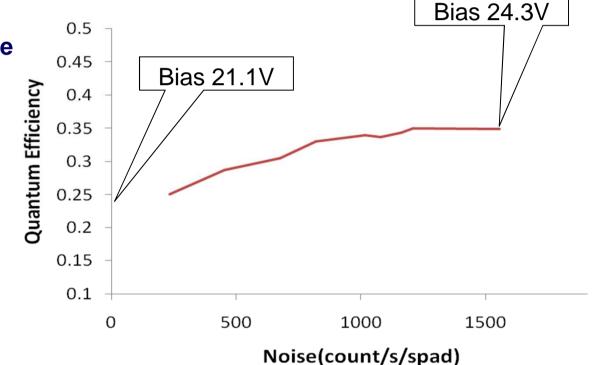

### **QE measurement II:**

## caeleste

#### Anode connected deep-junction SPAD

- Threshold voltage: 21.1 V

Over bias up to 3.2 V in the measurement

Max QE is 34.9%

Noise = dark count rate

- 660 nm laser

#### Outline

# Introduction: The SPAD principle Layout of SPAD and SPAD arrays Measurement results Conclusions

#### conclusions

#### Photon Conversion Efficiency (~QE)

- deep junctions, not shallow

- Deep well, deep and low doped epi layers

- Within the constraints of the CMOS technology

- design rules, available layers and implants

- It is possible to tune SPADs for a wide range of specifications using a standard CMOS technology

- It is found that available layers in the CMOS process can be used far outside their electrical specs.

#### Thank you

2 December 2013

Caeleste SPAD technology

25