# Radiation hard design in CMOS image sensors

Bart Dierickx, Caeleste CPIX Workshop 15-17 sept 2014, Bonn

### Outline

- Introduction

- Design for total dose

⇒Total ionizon dose TID

⇒Displacement damage DD

- Design for single events

⇒SEU single event upset

⇒SEL single event latch-up

- Take home message

Introduction TID total ionizing dose DD displacement damage SEU single event [upset...] SEL single event latch-up Take home message

### **Introduction** About us Background in Radhard CMOS design

### About us

### Founded 2006 Mechelen, Belgium 17p

Mission and business model

> Supplier of Custom designed Beyond "State of the Art" Image sensors

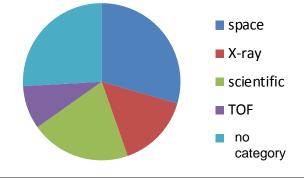

# Caeleste radhard background

### Where we come from

- ⇒Historical contribution to radhard and cryo design for space (ISOPHOT..., OISL, STAR250, HAS...)

- ⇒Background in design for particle physics and X-ray integrating and photon counting detectors

- $\Rightarrow$ Close relationships with foundry technologists

- $\Rightarrow$ Expertise in circuit & device physics & technology

Present

- $\Rightarrow$ Routine radhard design (TID, TnID, SE, SEL)

- $\Rightarrow$ Proton & SE hard pixels

- $\Rightarrow$ ROICs and image sensors

### Heritage

OISL 2000 first >10Mrad

QX 2010 Analog domain 2-energy "color" X-ray photon counting

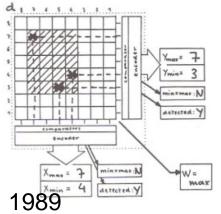

ISOPHOT FIR ROIC 1989 SEU hard wo TR

XYW event detector RD-19 SOI-CMOS 2013 wafer scale X-ray

STAR250/1000 2003

### Disclaimer

- This paper focuses on design countermeasures, while understanding the damage mechanism itself

- This is not a design course. Details of actual designs are not shown

- Technology countermeasures, temperature effects, annealing not treated

- No guarantee on effectiveness of techniques, nor of IP freedom

Introduction TID total ionizing dose DD displacement damage SEU single event [upset...] SEL single event latch-up Take home message

## TID total ionizing dose also referred to as IEL ionizing energy loss

radhard design in CMOS image sensors

### TID

Radiation:

$\Rightarrow$ Primarily X,  $\gamma$ , but essentially all particles

### Dominant effect :

- $\Rightarrow$  Creation of positive space charge in the SiO2 (SiN) dielectric layers

- $\Rightarrow$ Also: increase of interface states at Si-SiO2 interface

- Effect on CMOS circuits:

- $\Rightarrow\,$  Moderate shift of Vth,  $\mu$  degradation and 1/f noise increase

- ⇒ Parasitic S-D leakage via STI/field in nMOSFETs resulting in large dissipation and malfunction

### TID

### Effect on CMOS pixels:

- $\Rightarrow$  Moderate offset shift and 1/f noise increase

- $\Rightarrow$  Lateral shunting between pixels

- $\Rightarrow$  Lower gain and increased PRNU

- $\Rightarrow$  Increased average I<sub>dark</sub> and DNSU Most publications are describing this last effect

# Design countermeasures caeleste

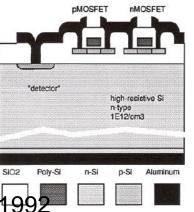

- Buried diodes as the general way to reduce dark current

- Avoiding the parasitic source-drain leakage in nMOSFETs

- Several case-by-case other measures

### **TID-hard CMOS**

Regular transistor

Leaks when STI/field inverts

Annular transistor: No path over STI/field

H-gate transistor: Leakage path over STI/field is blocked by P-implant

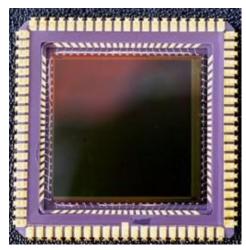

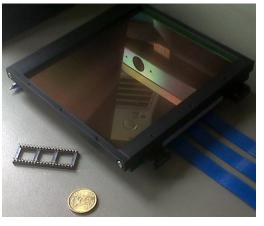

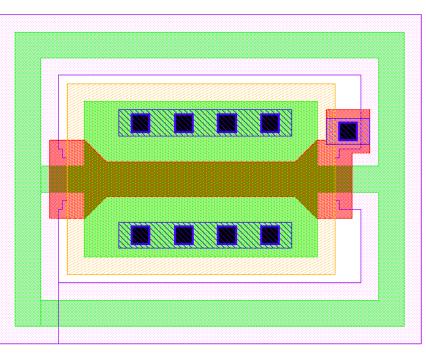

### The "CES" IR ROIC

Fully radhard & cryo<sub>77K</sub> UMC018 Digital: DARE library Analog: CaelesteRH >>1Mrad, not tested yet

caeleste

ESA consortium Caeleste+Easics+Selex 2014

radhard design in CMOS image sensors

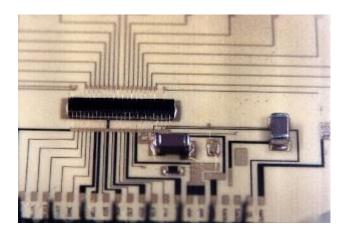

### 4 SAR ADCs, detail

radhard design in CMOS image sensors

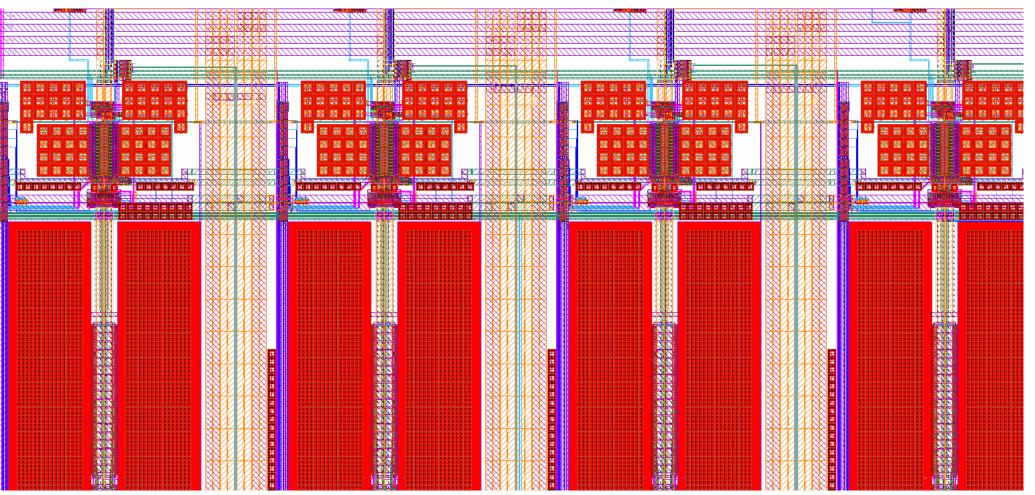

### Digital logic, detail

08 00 P.m.m. 88 601 000 80 8 m LB R Ella de po concepto de pa pace de pa de sens de ba concepto de palle secondo ace a 22 as la da avea an de sectores an as sult zaen bu ko sossasan ak an ommi ; ; 88 mesosse 86 88 6 88 6 besesan 12 0 00 00 0 **1 10 17 17 17 17 17 17 17** ----ne sons he as suddened ad to promme as as persons as as pone as c ee an UDD on D.ee Tr shas as as padraars as as all andres Clic an ad seconds on an adag of a sa sa 00 a asaasaas as 00 s sa aa asaa sa sa 00 4 # 00 00 #ee 00 9 ### 00 na as provinces an an issue as close and as 0 000 000 \*\*\*\* 30.0 0 bout at tobs at he desusand as an offer a at out as an engineers at the sole a se avera as as as concrete as as a set in a . . . . E 00 FFR P 00 00 0 22 0020 1 1 1 2 a 68 68 is 65 is 66 68 is 66 68 mmin Of De sourcens de bu janes be a . ... <u> 9 00 9 00 00 99 00 00 9</u> 0000 00 00 0000000 00 00 00 00 07 00 800 1 B B B an opag as on conceptor on an aller i at

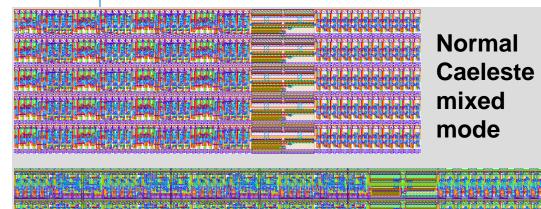

## Caeleste RH library

CaelesteRH as compared to SotA

- Available in 3 technologies, porting is standardized

- Full analog & mixed mode

- Very high TID & TnID hardness

- Very high SEL hardness

- Very high SEU hardness wo TR

- <20% increased Cin and power <50% area increase

Caeleste RH

caeleste

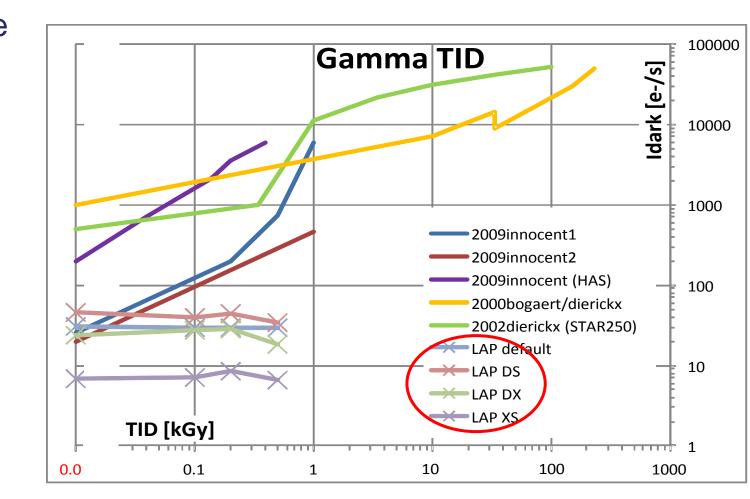

### TID Gamma Radhard pixels

LAP2010 device Tower TSL018 2011

TID of gamma <sup>60</sup>Co

Compared to published SotA

caeleste

radhard design in CMOS image sensors

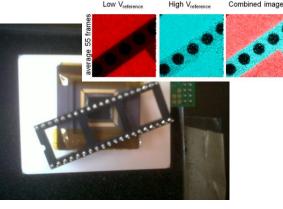

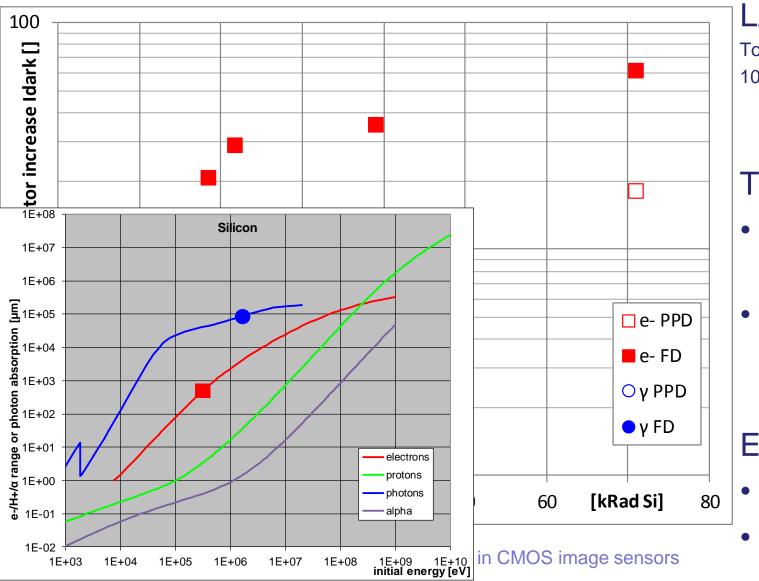

# TID Gamma ≠ Electrons Caeleste

LAP2010 device

Tower TSL018 10 devices; many pixels per device

### TID of

- 300keV electrons

- 1.2/1.3 MeV gamma <sup>60</sup>Co

### Effect on

- Buried PPD

- Surface FD

18

Introduction TID total ionizing dose DD displacement damage SEU single event [upset...] SEL single event latch-up Take home message

## DD displacement damage also referred to as "NIEL" non-ionizing energy loss

### DD

### Radiation:

- $\Rightarrow$ HE particles: protons and heavier

- Dominant effect :

- $\Rightarrow$ Non-elastic displacement of Si atoms

- $\Rightarrow$ Often creating an initial vacancy+interstitial

Effect on CMOS pixels:

- $\Rightarrow$  Point-wise heavily leaking diodes, hot pixels

- ⇒ Often blinking "RTS" dark current pixels

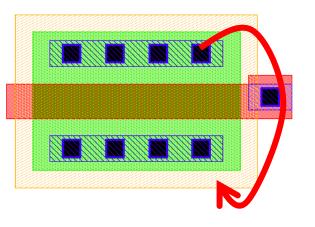

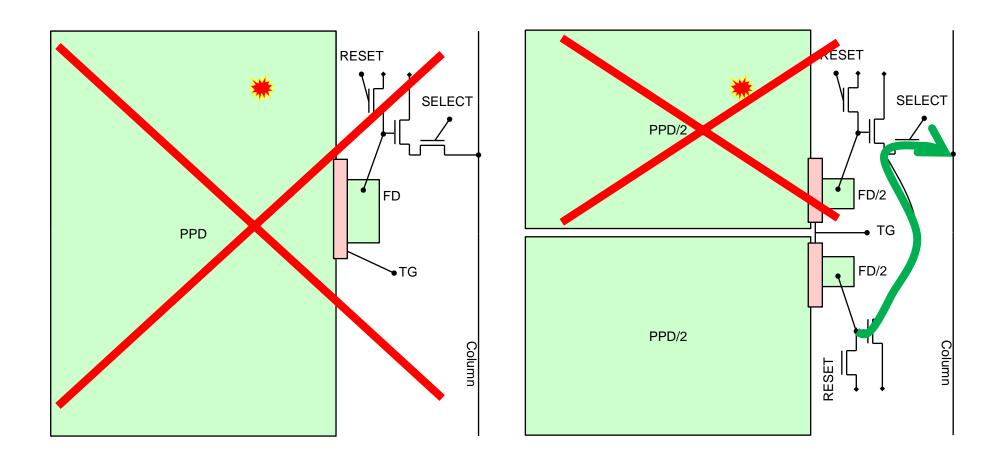

# Photodiode redundancy? caeleste

Proton/Neutron/other\_particle

- ⇒ displacement damage in the photodiode creates "hot" or "RTS" pixel

- $\Rightarrow$ SE creates flash

- No way to remove or calibrate this?

Suppose we split the pixel in 2...100 parts. The defect will reside in only one

Redundancy?

- $\Rightarrow$  Readout all, remove the defect part's signal and average.

- ⇒ Take a weighted maximum voltage by winner take all circuit or sourcefollower

radhard design in CMOS image sensors

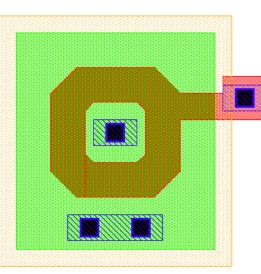

## Photodiode redundancy Caeleste

20140916

radhard design in CMOS image sensors

US patent US8426828

Introduction TID total ionizing dose DD displacement damage SEU single event [upset...] SEL single event latch-up Take home message

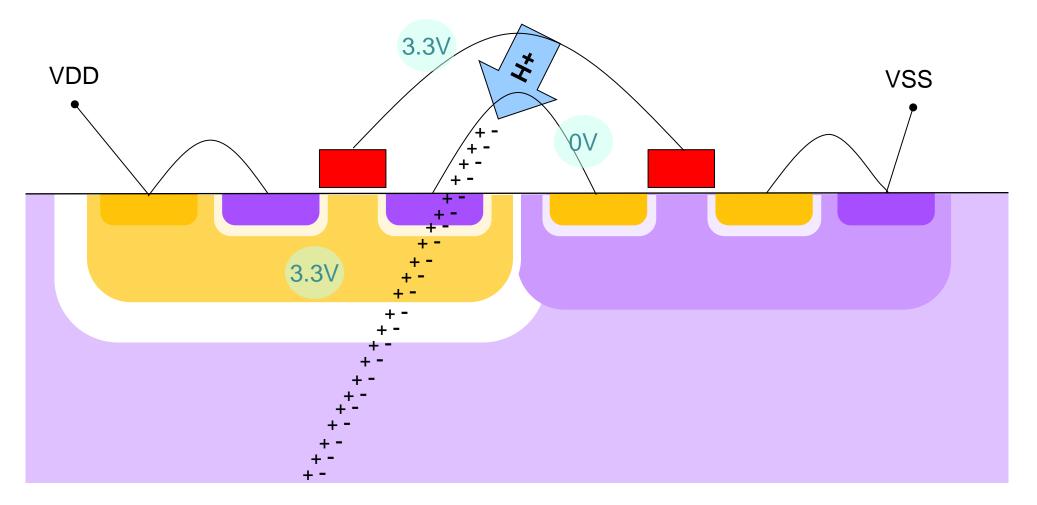

SEU

### **Single event** [upset] Also SEE, SEFI, SET, SEGR, SEB ... () SEL is separately treated

### SEU

### Radiation

$\Rightarrow$ Sometimes X,  $\gamma$ , e-, but rather much heavier particles

### Dominant effect :

- $\Rightarrow$ Creation of instantanous + or charge packet sufficient to toggle a latch

- Effect on CMOS and CMOS pixels:

- $\Rightarrow$  register or memory loosing information

- $\Rightarrow$  flash seen by the photodiode

### $\Rightarrow$ The loss of bits in SRAM cells or Flip-flops

#### radhard design in CMOS image sensors

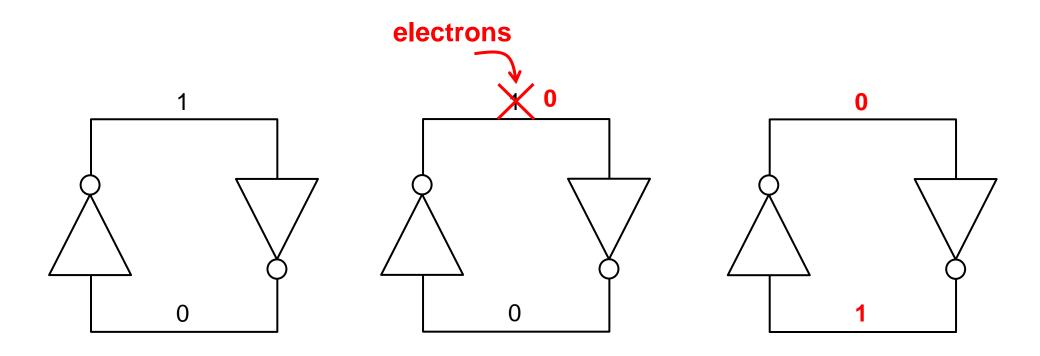

### SEU

### Mechanism

• Particle deposited charge packet charges one node of a latch to the oppisite logic value

### Flipping the invertor @t<sub>0</sub>

## **Caeleste** Flipping the invertor $@t_0+0.5ns$

### SEU countermeasures

- Shield against particles

- Make vulnerable volume small

- Make vulnerable node capacitance large

- Triple (and other froms of) redundancy

- Detectability, read-back, re-upload

caeleste

Introduction TID total ionizing dose DD displacement damage SEU single event [upset...] SEL single event latch-up Take home message

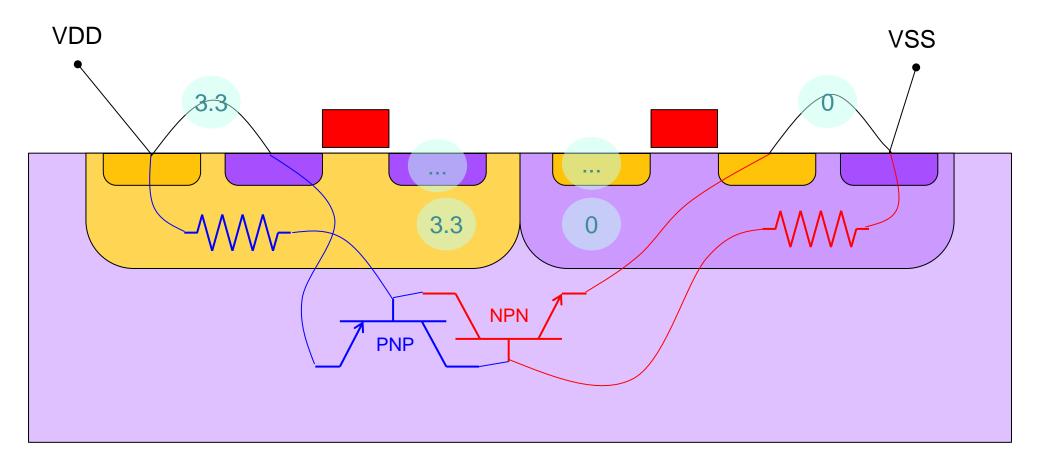

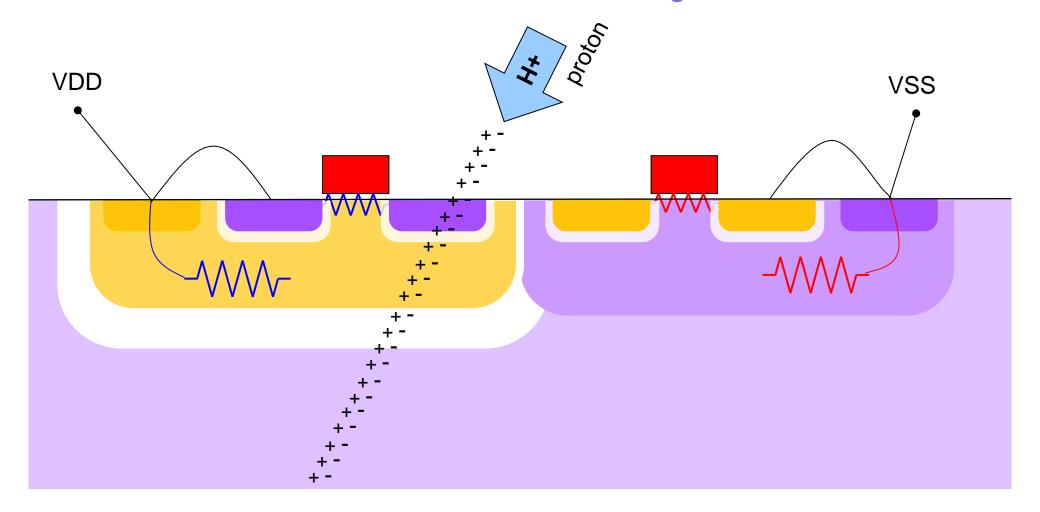

SEL

# single event latch-up

radhard design in CMOS image sensors

SEL

### Radiation

- $\Rightarrow$ Protons and rather even heavier particles

- Dominant effect :

- $\Rightarrow$ Creation of instantanous + or charge packet sufficient to initiate a PNPN latch-up

- Effect on CMOS:

- ⇒ Circuit collapsing and potential destruction due to excessive supply current

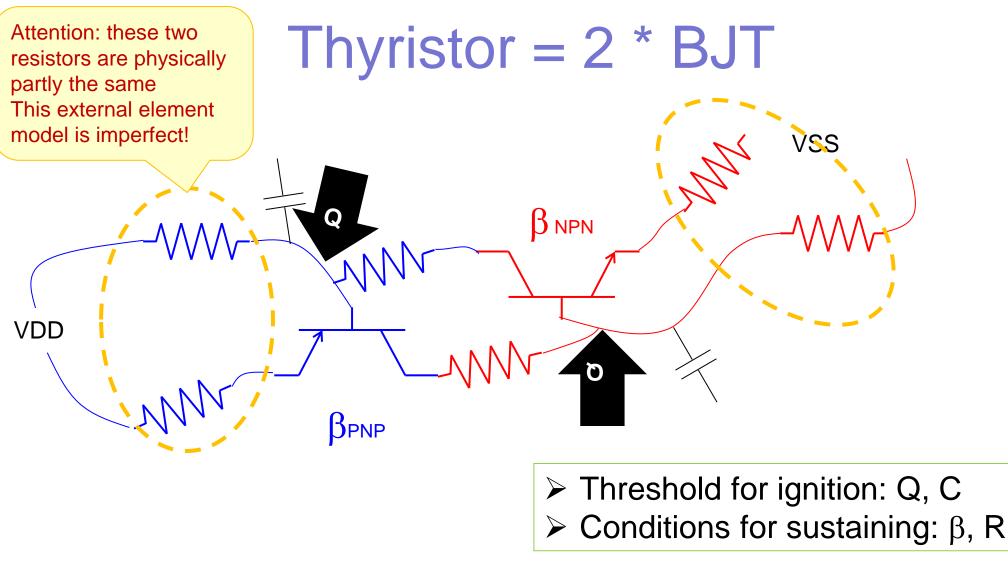

### Caeleste Bulk CMOS has an annoying thyristor

### Caeleste Bulk CMOS has an annoying thyristor

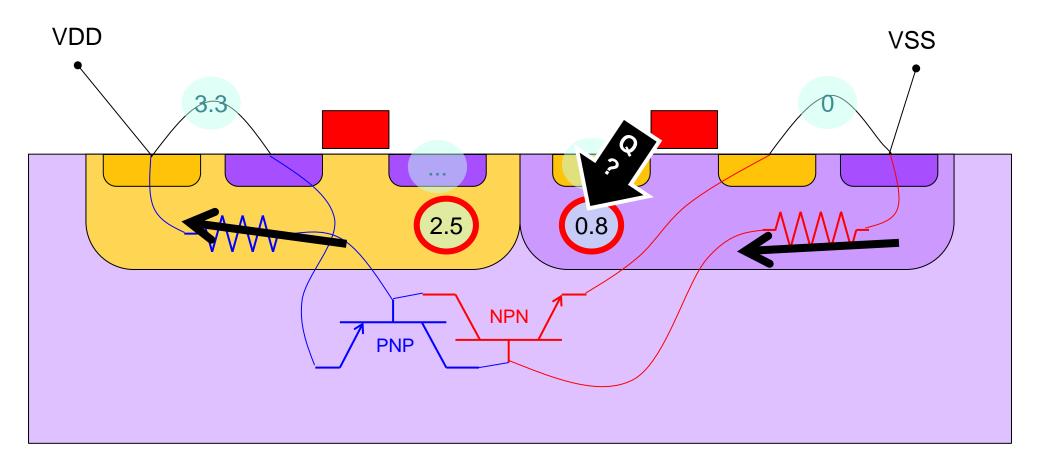

### Modeling SEL

### Quantitative compact (=SPICE) model?

$\Rightarrow$  Much better: a 3D device simulator.

### What lacks: value for series resistances

- $\Rightarrow$  Series resistances in E, B, C. Can estimate it from techology data.

- $\Rightarrow$  Pay attention that "resistance" applies to majority carriers. Base resistance is thus over/underestimated and partly uncorrelated

- $\Rightarrow$  Emitter and Base resistances partly overlap: Emitter current increases IR drop of Base.

### What lacks: models of the parasitic BJTs

$\Rightarrow \beta$ : must eventually "measure" that. Start with default value (100...1000) for "qualitative" estimate.

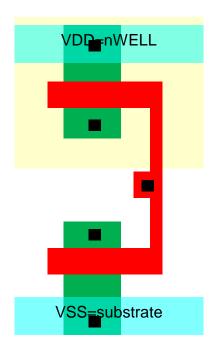

# Design countermeasures Caeleste

#### Avoid ignition

- $\Rightarrow$  minimize sensitive volume

- $\Rightarrow$  maximize C/Q: increase node capacitances

### Avoid sustaining

- $\Rightarrow$  Maximally reduce the series resistance in the thyristor

- $\Rightarrow$  Between the nWELL and pWELL: guard rings metallically tied to VDD/VSS

#### Avoid proliferation

⇒ nWELLs (actually the well not being the substrate) should be fragmented. So that the latchup remains confined: when one section latches, the general supply voltage does not collapse.

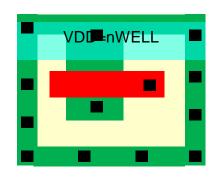

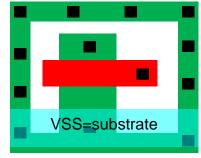

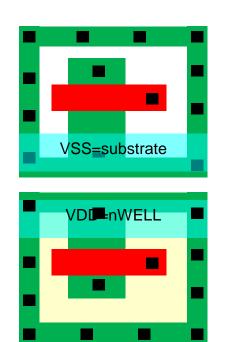

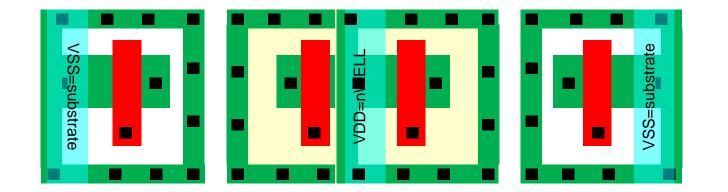

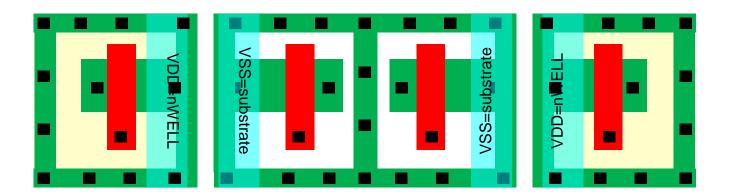

### **Design style**

Classic CMOS design style

#### Metal guardring around wells

#### Rails in the middle

#### radhard design in CMOS image sensors

### Mirrored rails

•••

20140916

#### radhard design in CMOS image sensors

0 0

0 0

### **Technology measures**

#### Avoid the thyristor

$\Rightarrow$  SOI, FinFET

#### Reduce the bipolar feedback

- Poor BJTs

- $\Rightarrow$  Trenches

- $\Rightarrow$  Low sheet resistances

- $\Rightarrow$  Epi wafers (p- on p++ or n- on n++): reduces 1 Base resistor

- $\Rightarrow$  Increased recombination  $\rightarrow$  reduces minority current and increases I<sub>dark</sub>

#### Reduce the pick-up

$\Rightarrow$  Small charge collecting volume in the Bases

### Triple well...

#### The number of *possible* thryristors increases

### Good to know

# nMOS-only or pMOS-only circuit parts cannot latchup.

A standalone BJT does not latchup

# SEL and vulnerable nodes

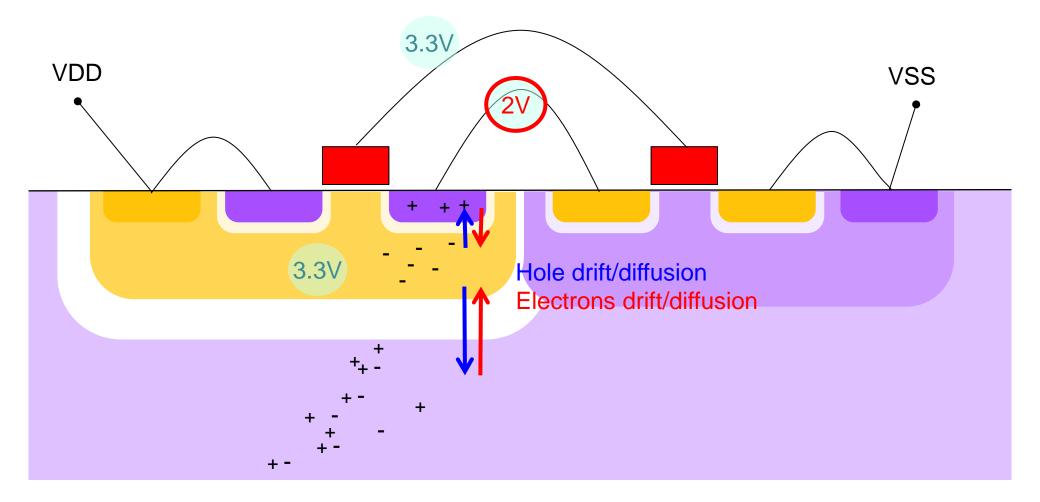

⇒ How much charge is deposited on a vulnerable node

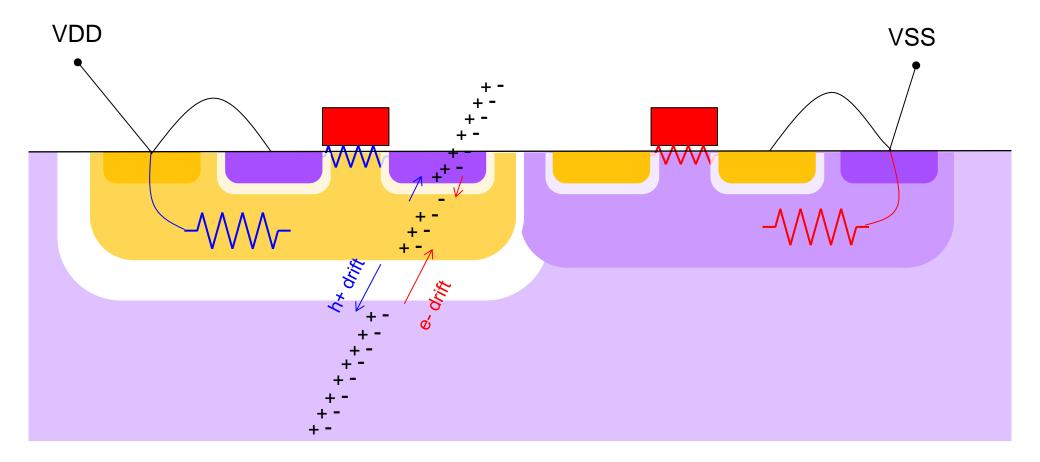

### Vulnerable volume @t<sub>0</sub>

# **Caeleste** Vulnerable volume @t<sub>0</sub>+10ps

# Caeleste Vulnerable volume $@t_0+0.5ns$

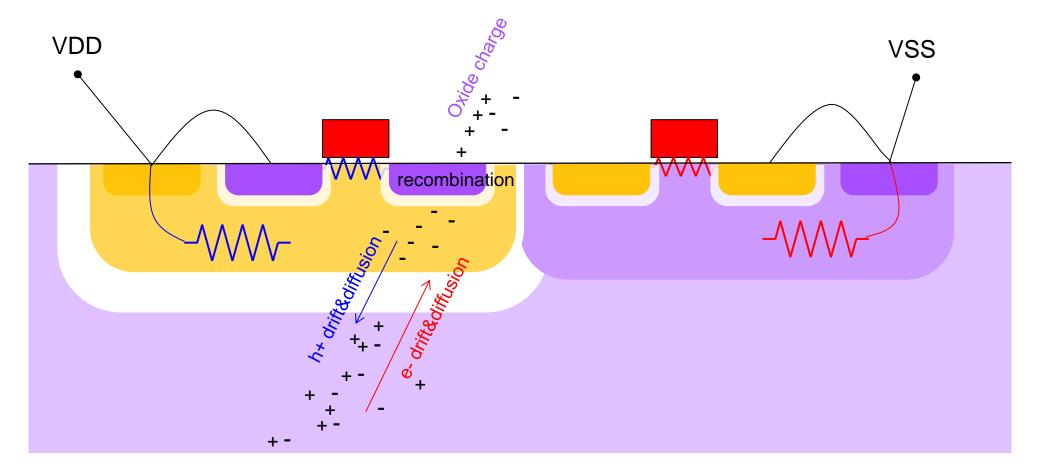

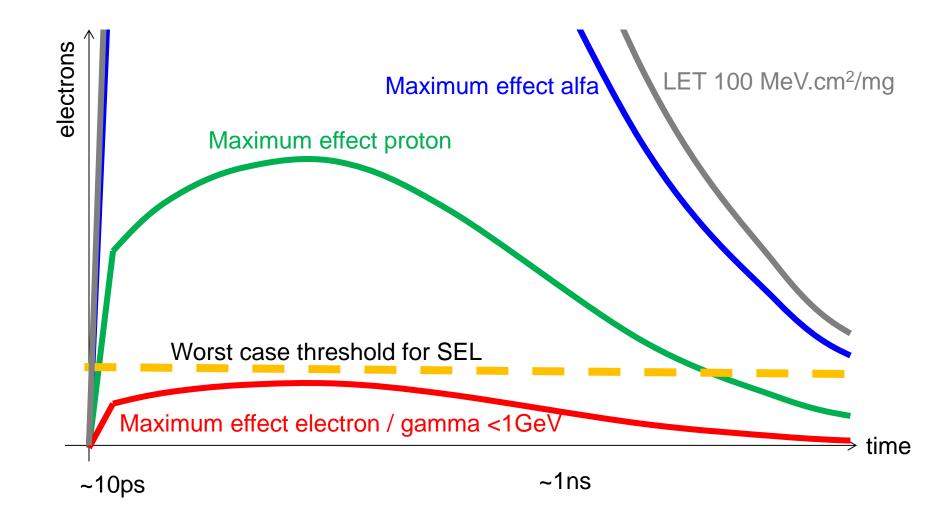

### Net node charge as function of time the nWELL case

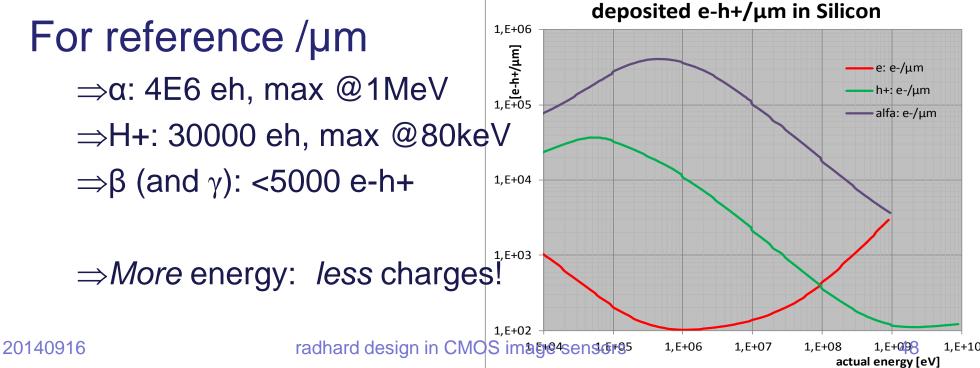

# How to estimate Q? Caeleste LET linear energy transfer

Heavy ions are commonly described by amount of energy lost per unit track length = Linear Energy Transfer

#### Linear Energy Transfer

- $\Rightarrow$  Energy loss per unit path length

- $\Rightarrow$  dE/dx= MeV/cm

- $\Rightarrow$  Divide by material density = MeV.cm<sup>2</sup>/mg

- $\Rightarrow$  LET of 100 MeV.cm<sup>2</sup>/mg corresponds to charge deposition of 1pC/µm = 6E6 e-/h+

#### How does LET spectrum relate to the real space environment?

- $\Rightarrow$  A measure for the heaviest ions/events that can be expected

- $\Rightarrow$  Says nothing about number of particles or probability

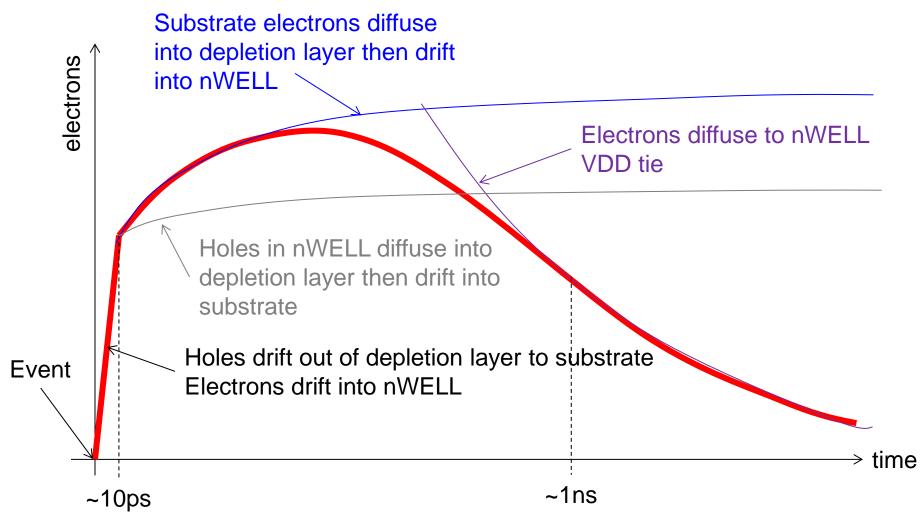

### e-h+ pairs per µm

#### 100 MeV.cm<sup>2</sup>/mg ≈ 1pC/µm = 6Me-h+/µm

$\Rightarrow$ This is a linear function, thus 50 MeV.cm<sup>2</sup>/mg is still 3 million charges/µm.

#### Voltage drop assuming instantanous charge deposition

#### Minimal junction size and capacitance $\Rightarrow$ 1fF & 1µm: 6000 e- = 1V $\Rightarrow$ Electrons (hence gamma) cannot create V<sub>forward</sub> $\Rightarrow$ Protons can (marginally) ignite LU Proton SEL hard junction? $\Rightarrow$ 5fF & 1µm: 30000 e- = 1V. Yet, shallow angle?

### Net node charge as function of time

caeleste

Introduction TID total ionizing dose DD displacement damage SEU single event [upset...] SEL single event latch-up Take home message

# Take home Message conclusions

### Take home

CMOS imagers can be made hard against TID, SEL, SEU etc by design  $\Rightarrow$ TID: avoid field leakage  $\Rightarrow$ SEL: reduce bipolar feedback  $\Rightarrow$ SEU: vulnerable volume & circuit redundancy Photodiode hardening for SE and displacement damage remains a question

• Photodiode redundancy?

caeleste

#### Thank you