10

# Rad-hard image sensors area/power/hardening trade-offs

B.Dierickx, <u>P.Gao,</u> Q.Yao, B.Luyssaert, K.Liekens, A.Kumar Kalgi, S.Veijalainen, W.Wang Caeleste, Mechelen, Belgium

## Outline

## caeleste 10

- Motivation

- A short summary of radiation effects

- A short summary of counter measures

- Countermeasure effect on area, speed and power

- Take home messages

## Chapter 1 MOTIVATION

## Purpose

- caeleste 10

- Overview of actual radiation hard circuits

- Direct comparison with the non-radhard equivalents.

- For image sensors and their periphery circuits.

- Focus on different type of radhardness and their impact on area, speed and power

- <u>Not</u> touch the actual hardness levels achieved nor pixel radhard design

## Example

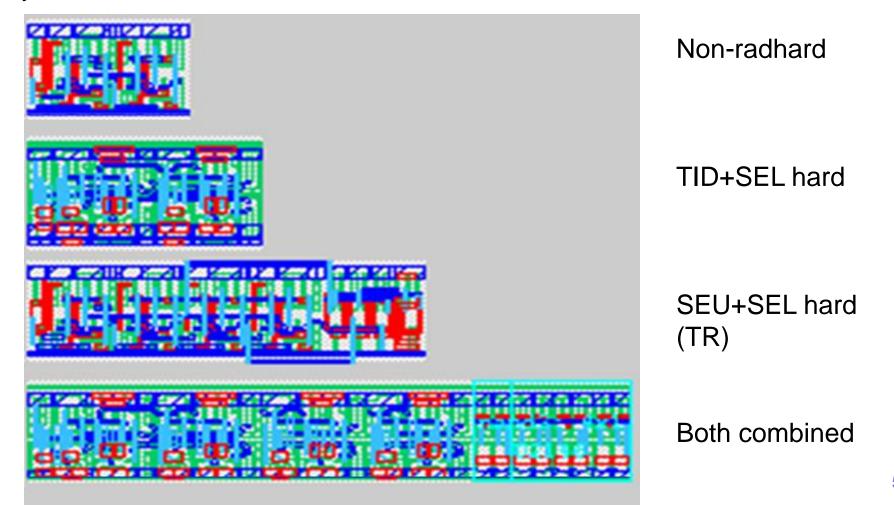

A common logic block: different level of radiation hardness.

As each of these are different in approach and effect, this is rather a case study than a systematic overview.

caeleste

1()

## Caeleste SE hard and not TID hard? 10

It is perfectly possible – and this actually makes sense – to design purely for SEL (single event latch-up) hardness, and disregards the other forms of hardness.

SEL hardness usually does not require a large area penalty in image sensors, whereas for many mission types it is the only damage mechanism that may be threatening for the mission.

## Chapter 2 SHORT SUMMARY OF RADIATION EFFECTS

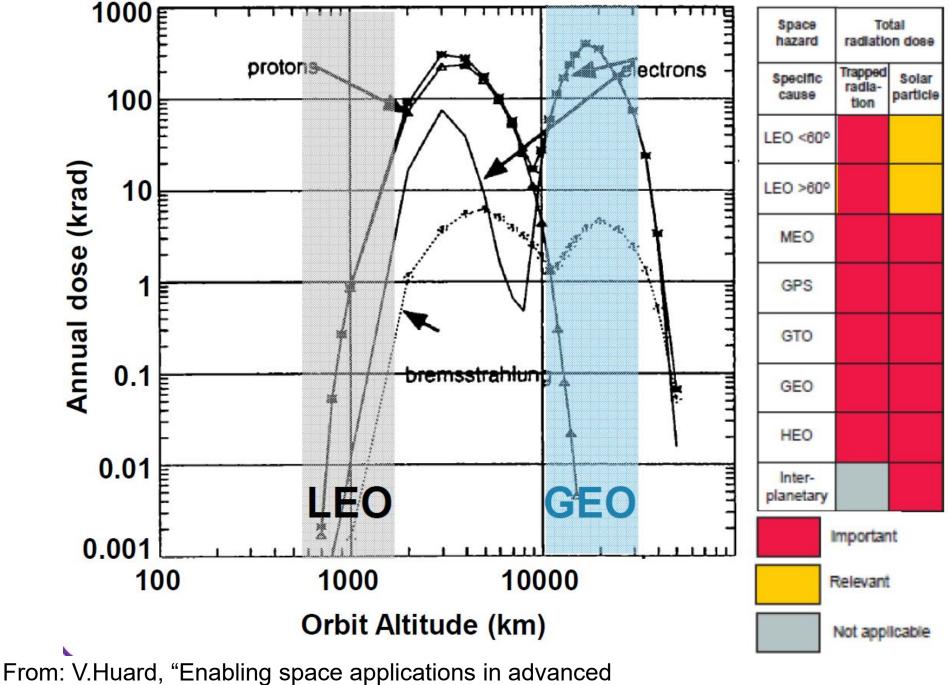

Van Allen belts: High-energy electrons and protons Trapped in the Earth's magnetic field

Outer Belt 12,000 — 25,000 miles

> GPS Satellites 12,500 miles

> > Geosynchrono

Inner Belt \_\_\_\_\_ 1,000 — 8,000 miles

> Low-Earth Orbit (LEO) International Space Station 230 miles

> > Van Allen Probe-A

© NASA website

Van Allen Probe-B

CMOS nodes: challenges and oportunities", March 1, 2016

# SEE(Single event effects) Caeleste 10

- SEU single event upset

- SEL single event latch-up

- There exist many more "SE"s, such as SEGR

- Which are typically rare or irrelevant in CMOS

- Have no countermeasure except shielding or the SEU/SEL counter measures already in place

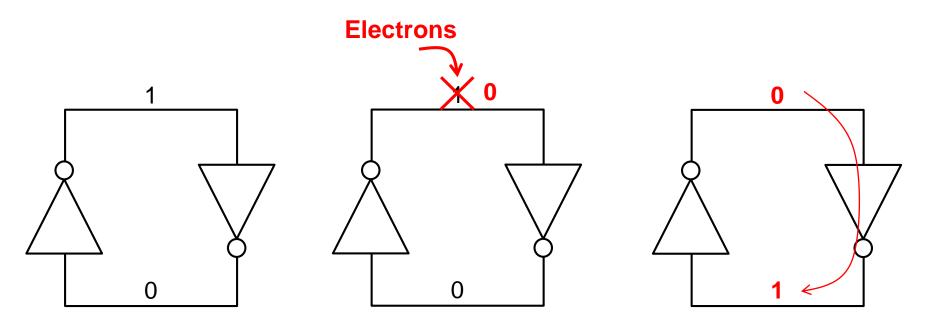

## SEU

## caeleste 10

## Corruption of bit in SRAM or Flip-flop

- $\Rightarrow$ Charge packet deposited by particle charges

- $\Rightarrow$ One node of a latch to the opposite logic value

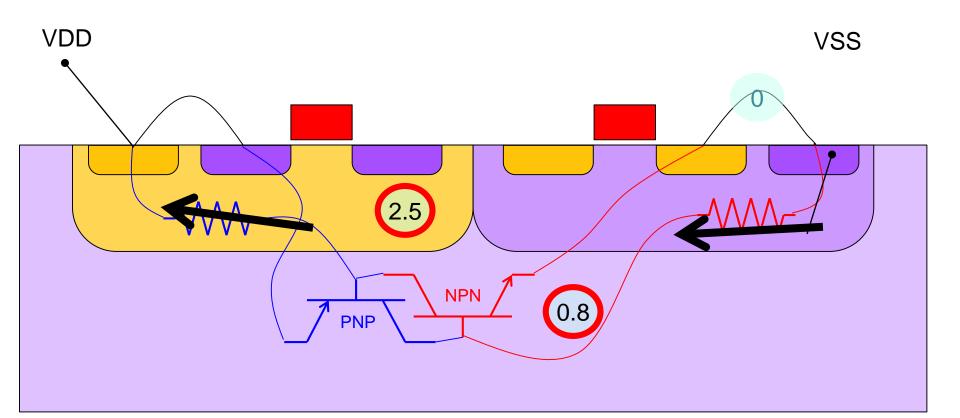

SEL

## caeleste 10

# High energy particals tuned on the parasitc thyristor of bulk silicon ⇒power supply shorts

# TID (total ionizing dose) Caeleste 10

Radiation:

$\Rightarrow$ X,  $\gamma$  ,charged particles

Dominant effect :

- $\Rightarrow$ Positive space charge in dielectric layers

- $\Rightarrow$ Increase of interface states at Si-SiO<sub>2</sub>

Effect on CMOS circuits:

- $\Rightarrow$  Moderate degradation of Vth,  $\mu$  and 1/f noise

- $\Rightarrow$  Parasitic S-D leakage in nMOSFETs

## Chapter 3 SHORT SUMMARY OF COUNTER MEASURES

## TID-hard nMOSFET avoid the parasitic S-D leakage

Regular transistor

Leaks when STI/field inverts due to positive charge built-up due to ionizing radiation

Annular transistor: No path over STI/field

H-gate transistor: Leakage path over STI/field is blocked by Pimplant

caeleste

## **TID** countermeasures

- Minor effect 883

- Adequate Helps

- Shield against radiation

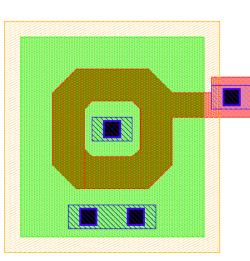

- **Ring MOSFETs**

- **H MOSFETs**

- SOI/FINFET

- Defensive circuit design

caeleste

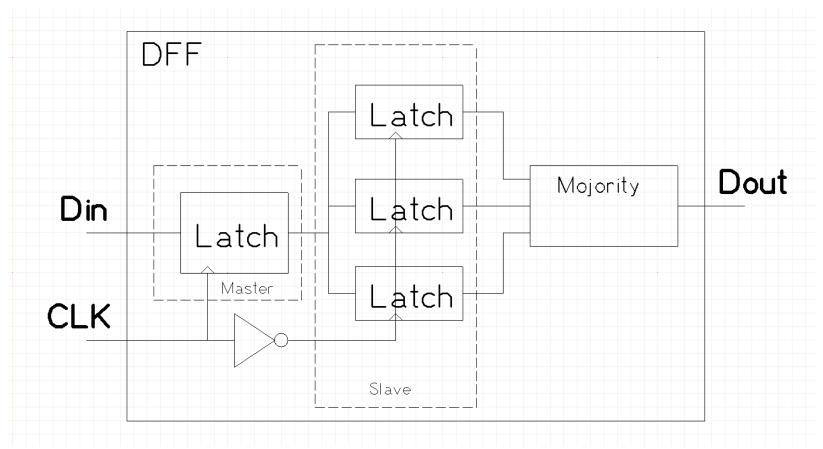

## SEU Design countermeasures using TR Triple-redundant-slave flipflop

2016 11 16

rad-hard design trade-offs

# SEU countermeasures Caeleste

Some effect Adequate Helps Shield against particles ۲ Make vulnerable volume small Make vulnerable node capacitance large ۲ Triple (and other forms of) redundancy ٠ Detectability, read-back, re-upload ۲

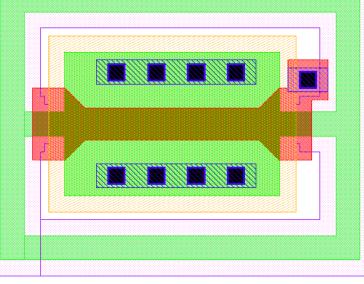

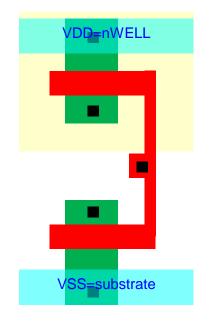

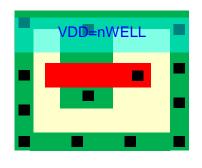

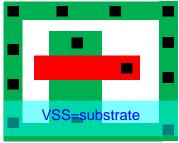

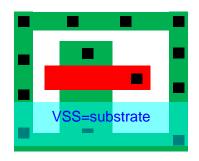

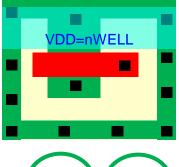

# SEL Caeleste 10 Design counter measures using guard rings

## Classic CMOS design style

••

## Metal guardring around wells

### Rails in the middle

# SEL countermeasures

## Avoid ignition

- $\Rightarrow$  Reduce pick-up: minimize sensitive volume

- $\Rightarrow$  maximize C/Q: increase node capacitances

- $\Rightarrow$  No thyristor: SOI, nMOS only, FINFET

## Avoid sustaining

- $\Rightarrow$  Reduce the series resistance in the thyristor

- $\Rightarrow$  guard rings metallically tied to VDD/VSS

### Avoid proliferation

- $\Rightarrow$  Fragment nWELLs

- $\Rightarrow$  Detect & reboot

Adequate

caeleste

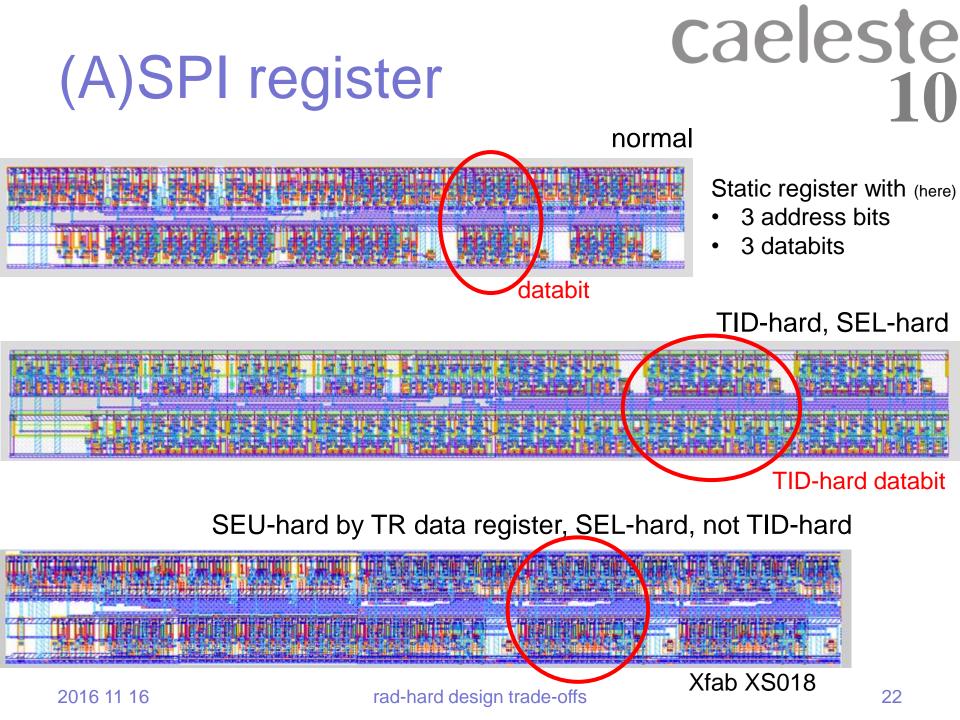

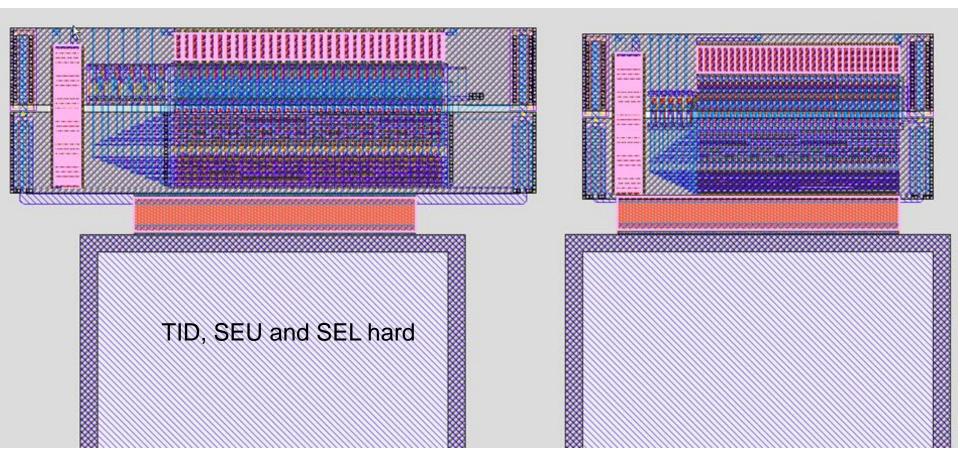

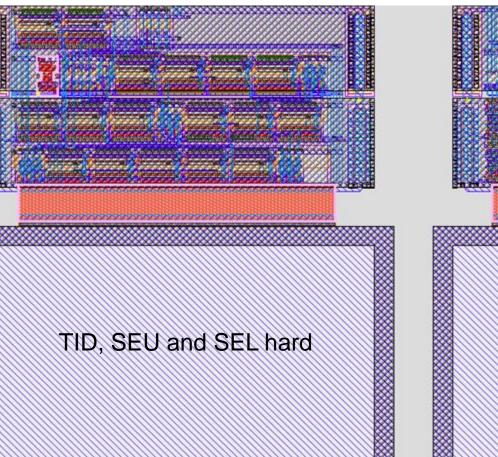

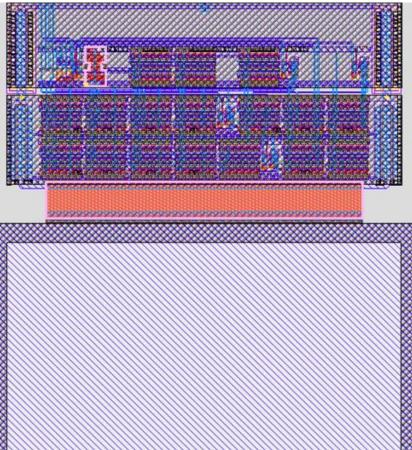

## Chapter 4 LAYOUT EXAMPLES

rad-hard design trade-offs

#### 2016 11 16

#### rad-hard design trade-offs

#### 23

caeleste

10

## IO rail RDAC

# IO rail programmable bias Caeleste

### rad-hard design trade-offs

### 2016 11 16

#### rad-hard design trade-offs

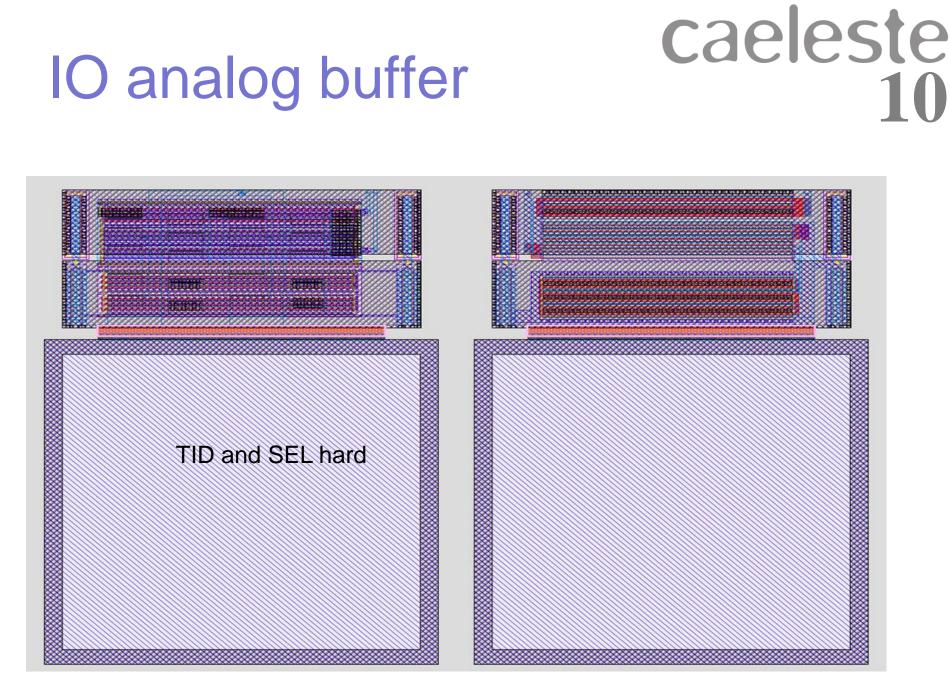

# Cost of hardening

"normal"

- Not TID hard

- No specific SEL precautions

- No TR

Area x 1.0 ... 1.5 Power x 1.0 ... 1.5 Speed x 1.0 ... 0.5

### TID-hard

Specific TID countermeasures

caeleste

• SEL countermeasures

### SEU-hard

- Not TID hard

- No specific SEL precautions

TR slave:

Area x 1.5

TR full

Area x 2

For register part

TR in register bit slaves

### 2016 11 16

### TID&SEU

- Specific TID countermeasures

- SEL countermeasures

- TR in register bit slaves

## Chapter 5 TAKE HOME MESSAGE

rad-hard design trade-offs

## Take home message

Total Dose (Ionizing and Displacement damage)

- $\Rightarrow$  High radiation hardness can be designed for

- $\Rightarrow$  Weak points remains I<sub>dark</sub>

- Single Events(mainly SEU and SEL)

- $\Rightarrow$  Nearly perfect protection against SEU and SEL can be designed for.

- $\Rightarrow$  Remains weak for: very heavy ions

- $\Rightarrow$  Inherent weak point: the pixel itself is made to detect radiation.

- Independent TID and SEE hardness

- $\Rightarrow$  Can be independent implemented.

- ⇒ Trade off depends on mission type, duration, shielding conditions, FEE intelligence...

caeleste

## References

- caeleste 10

- V.Huard, "Enabling space applications in advanced CMOS nodes: challenges and oportunities", March 1, 2016

- Bart Dierickx, Jan Vermeiren, Dirk Van Aken, Dirk Uwaerts, Peng Gao, Ajit Kumar Kalgi, "Image sensors in Space applications", presentation at the Fraunhofer IMS workshop, 10 May 2016, Duisburg

- B.Dierickx, "Radiation hard design in CMOS image sensors", CPIX Workshop 15-17 sept 2014, Bonn

- P Gao, B Dupont, B Dierickx, E Müller, G Verbruggen, S Gielis, R Valvekens, "Cryogenic and Radiation Hard ASIC Design for Large Format NIR/SWIR Detector Array", ISCO conference, 2014

## Thank you!