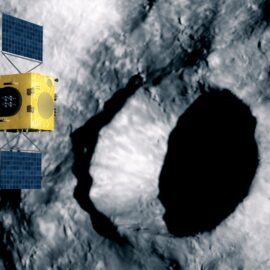

On March 27th 2024, Caeleste welcomed a diverse group of enthusiastic engineers to the Caeleste Pixel Experience 2024! This year’s theme: Pixels in Hyperspectral Sensors. Over the course of the afternoon, our guests received a welcome and introduction to Caeleste, tutorials

KU Leuven Micro-Credential Course on Analog Layout 2024

The MICAS (KU Leuven) Micro-Credential Course on Analog Layout concluded this week at KU Leuven ESAT-MICAS, taught by industry experts from ICsense, SOFICS, OMNIVISION, Cyient, and Caeleste. Organised by Prof. Patrick Reynaert, the course offered the opportunity to learn from industry experts in the microelectronics